怎么在RTL级别电路建模优化congestion问题

怎么在RTL级别电路建模优化congestion问题,针对这个问题,这篇文章详细介绍了相对应的分析和解答,希望可以帮助更多想解决这个问题的小伙伴找到更简单易行的方法。

成都创新互联主要从事成都网站制作、网站建设、外贸网站建设、网页设计、企业做网站、公司建网站等业务。立足成都服务塔城,10年网站建设经验,价格优惠、服务专业,欢迎来电咨询建站服务:18980820575

数字IC设计可谓环环相扣,很多环节都存在迭代发生的可能。

在最初芯片设计之前主要考虑PPA,即power、performance和area,但是实际项目中还存在仿真、测试及后端实现的问题。

下面主要介绍RTL设计引入的后端实现过程中的布线(routing)问题。

后端物理实现需要完成芯片中布局布线(place&routing)的工作。在物理实现过程中routing之前的floorplan阶段、placement阶段和CTS阶段都对routing效果有很大的影响,也有很多针对congestion的优化技术。

但是,实际项目中依然存在走线无法绕通的问题,可能是因为芯片对利用率要求可能比较苛刻,也可能是因为在RTL级别建模电路时造成了难绕线问题。

芯片物理实现中的macro走线、电源布线等占据走线资源,时序和串扰也会给走线引入更多的问题,我们应该尽量减少由RTL级别电路建模引入的无法走线问题。

下面举两个在RTL级别优化电路走线问题的示例:

1、大扇入

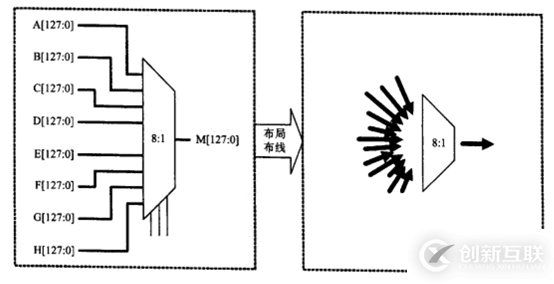

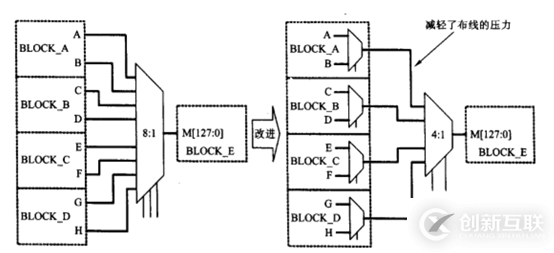

reg [2:0] SEL ;reg [127:0] A,B,C,D,E,F,G,H, SEL;always@(*) begin case(SEL) 2’b000:M <= A ; 2’b001:M <= B; 2’b010:M <= C ; 2’b011:M <=D ; 2’b100:M <= E ; 2’b101:M <= F ; 2’b110:M <= G ; 2’b111:M <= H ;endcaseend

在上面的电路中一个MUX电路具有非常大的扇入(8X128=1024)。可以通过级联MUX优化走线问题:

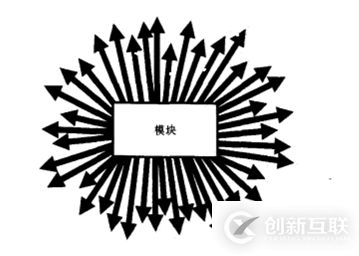

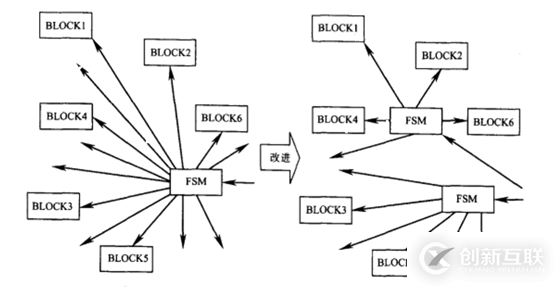

2、大扇出

设计中还存在一种被广泛使用的信号,这种信号具有非常大的扇出,例如时钟、复位和使能等。

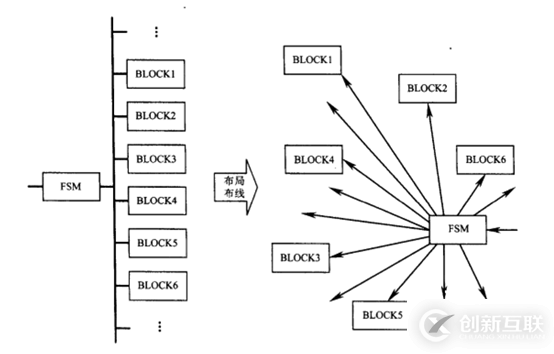

为了解决这个问题,可以复制信号源。这也体现了利于走线和硬件开销之间的折中。

上面这个有限状态机输出信号被多个模块使用,可以复制这个状态机,优化走线问题。

关于怎么在RTL级别电路建模优化congestion问题问题的解答就分享到这里了,希望以上内容可以对大家有一定的帮助,如果你还有很多疑惑没有解开,可以关注创新互联行业资讯频道了解更多相关知识。

新闻标题:怎么在RTL级别电路建模优化congestion问题

文章转载:https://www.cdcxhl.com/article4/iedsie.html

成都网站建设公司_创新互联,为您提供外贸建站、定制网站、搜索引擎优化、小程序开发、ChatGPT、App开发

声明:本网站发布的内容(图片、视频和文字)以用户投稿、用户转载内容为主,如果涉及侵权请尽快告知,我们将会在第一时间删除。文章观点不代表本网站立场,如需处理请联系客服。电话:028-86922220;邮箱:631063699@qq.com。内容未经允许不得转载,或转载时需注明来源: 创新互联

- 商城网站必备的四大功能 2021-04-20

- 商城网站如何做才能吸引客户 2023-01-04

- 简单的外贸商城网站建设 2023-02-19

- 上海商城网站建设如何才能吸引顾客停留? 2020-12-22

- 免费的微商城小程序到底靠不靠谱? 2014-02-08

- 企业如何运营电商商城网站网页制作开发平台 2021-03-03

- 如何搭建网上商城系统? 2015-09-13

- 创新互联对多语种外贸商城网站建设的解决方案 2014-05-25

- 网站建设时商城网站与普通网站有哪些不同之处 2016-10-27

- 武汉网站建设 | 商城网站的主要功能解析 2022-07-18

- 企业建一个展示型网站还是商城网站呢? 2021-06-05

- 电子商城网站如何创建? 2014-07-31