FPGA中Retiming原理是什么

本篇内容介绍了“FPGA中Retiming原理是什么”的有关知识,在实际案例的操作过程中,不少人都会遇到这样的困境,接下来就让小编带领大家学习一下如何处理这些情况吧!希望大家仔细阅读,能够学有所成!

公司主营业务:网站建设、成都网站建设、移动网站开发等业务。帮助企业客户真正实现互联网宣传,提高企业的竞争能力。创新互联公司是一支青春激扬、勤奋敬业、活力青春激扬、勤奋敬业、活力澎湃、和谐高效的团队。公司秉承以“开放、自由、严谨、自律”为核心的企业文化,感谢他们对我们的高要求,感谢他们从不同领域给我们带来的挑战,让我们激情的团队有机会用头脑与智慧不断的给客户带来惊喜。创新互联公司推出宜丰免费做网站回馈大家。

1 Retiming的定义

重定时(Retiming)是一种时序优化技术,用在不影响电路输入/输出行为的情况下跨组合逻辑寄存器从而提高设计性能。

2 Retiming的目的

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

3 Retiming原理

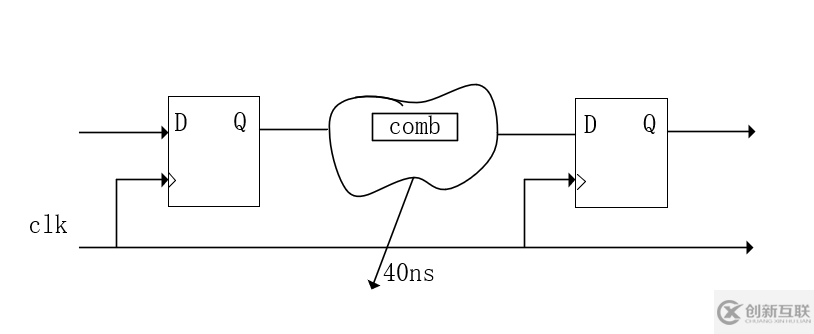

我们知道任何的数字电路都可以等效成组合逻辑加D触发器打拍,两个D触发器之间的组合逻辑路径决定了,系统的工作频率,决定芯片的性能。所以为了提高芯片的工作频率,使用流水线技术在组合逻辑中插入寄存器。

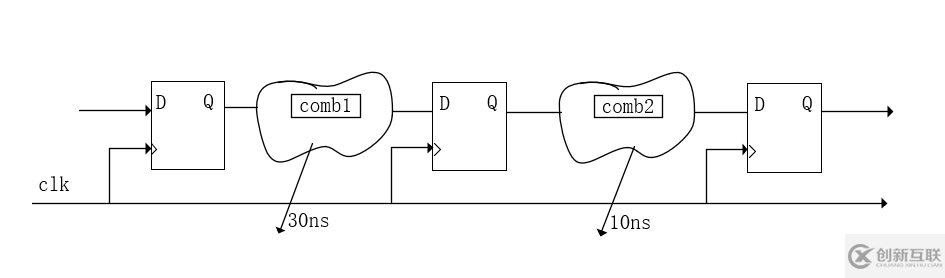

插入寄存器的位置需要慎重选择,不同的位置数据的打拍所消耗的寄存器的数量也不同,比方说你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省则省。

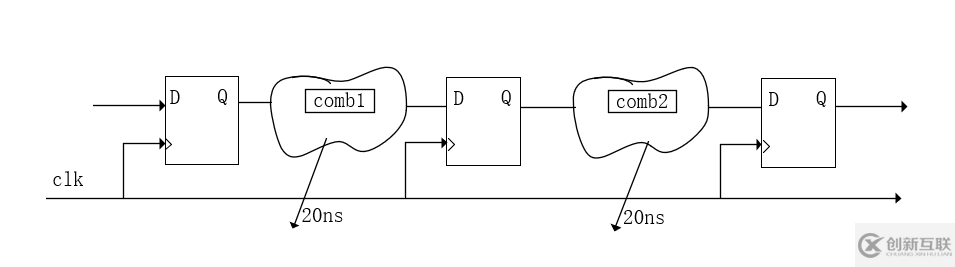

前面插入寄存器的位置使得comb1的延迟为30ns,comb2的延迟为10ns,系统的最高工作频率是由最长路径决定的。也就是说你这个系统最高工作频率的周期,不小于30ns,前面是插入pipeline,这个时候我们不改变时序,采用重定时技术,使得各个组合逻辑之间的延迟相当。

4 Vivado与Retiming

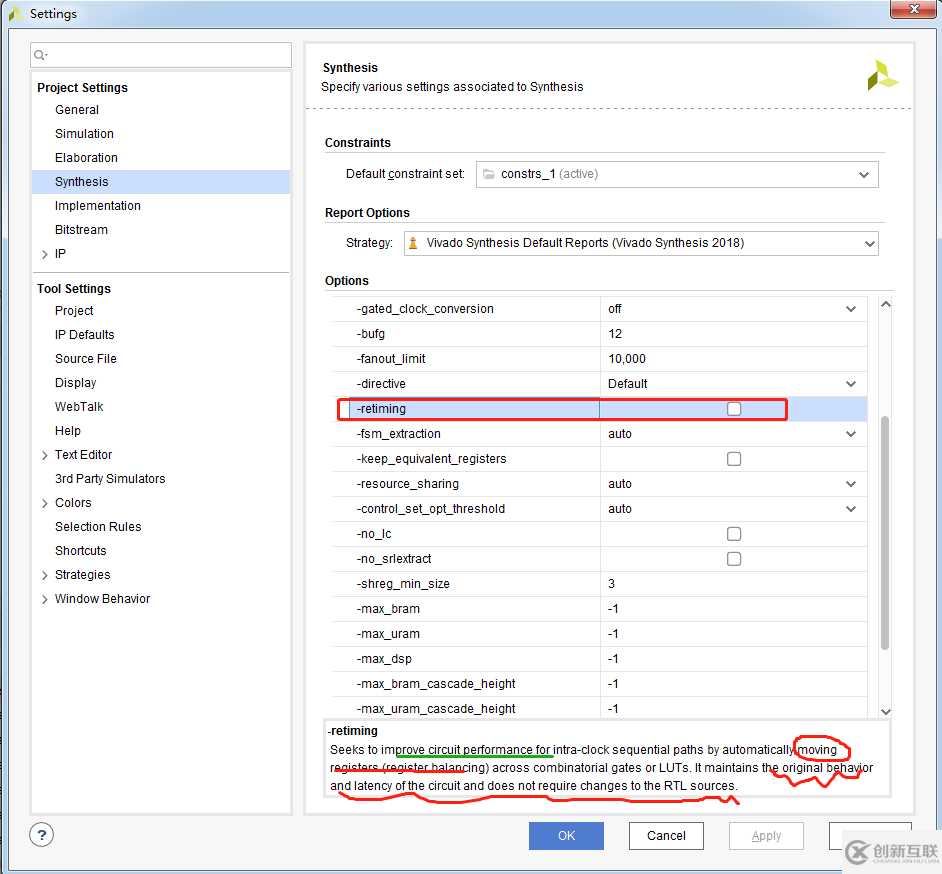

在Vivado 综合操作中有两种方法实现自动重定时(全局定时器),全局重定时是对整个设计而言的,基于设计时的时序要求优化大型组合逻辑结构中的寄存器设计。

这种方式需要分析设计中的所有逻辑,优化最坏路径情况下的寄存器从而使整体设计反应速度更快。为了实现这一点设计时必须在.xdc文件中规定准确的时间限制。在synth_design或Vivado GUI综合设置下通过-retiming命令启用全局重定时,此外该特性还可以与合成中的BLOCK_SYNTH特性一起用于设计中的特定模块。

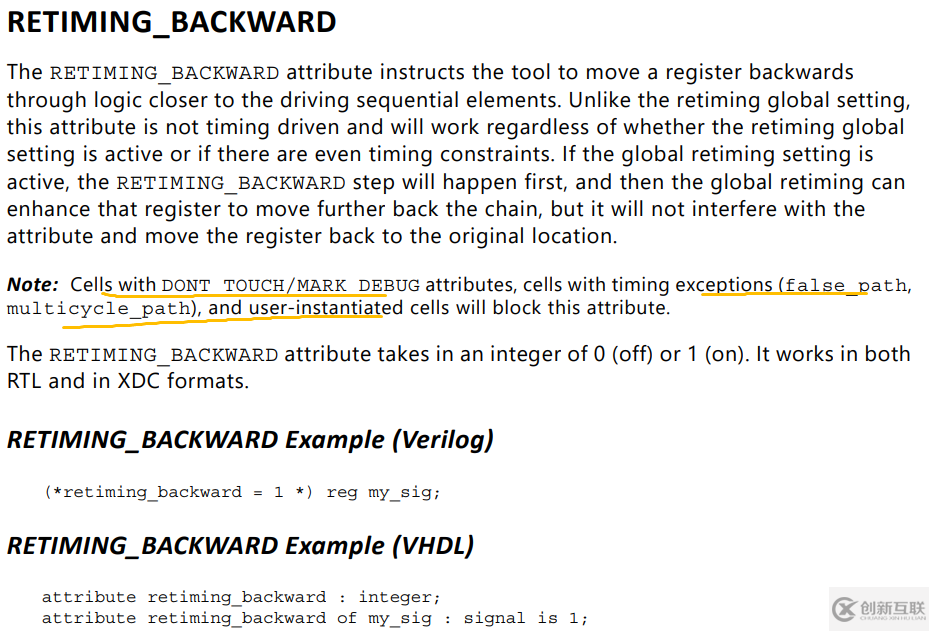

局部重定时是指用户明确告诉工具使用retiming_forward、retiming_backward RTL属性时需要执行的重定时逻辑。执行局部重定时操作是应该要小心,因为它不是计时器驱动的,而是工具将完全按照用户要求去执行。如下图所示(UG901)

如果是retiming_forward,只需要将(*retiming_backward = 1 *) reg my_sig;修改为(*retiming_forward = 1 *) reg my_sig;

注意以下情况下不能进行Retiming操作:

寄存器时序异常(多循环路径、错误的路径、最大延迟路径)

寄存器的类型属性不能改变(DONT_TOUCH, MARK_DEBUG)

采用不同控制级的寄存器

“FPGA中Retiming原理是什么”的内容就介绍到这里了,感谢大家的阅读。如果想了解更多行业相关的知识可以关注创新互联网站,小编将为大家输出更多高质量的实用文章!

分享题目:FPGA中Retiming原理是什么

路径分享:https://www.cdcxhl.com/article14/iipdde.html

成都网站建设公司_创新互联,为您提供域名注册、做网站、服务器托管、品牌网站制作、小程序开发、全网营销推广

声明:本网站发布的内容(图片、视频和文字)以用户投稿、用户转载内容为主,如果涉及侵权请尽快告知,我们将会在第一时间删除。文章观点不代表本网站立场,如需处理请联系客服。电话:028-86922220;邮箱:631063699@qq.com。内容未经允许不得转载,或转载时需注明来源: 创新互联

- 网站虚拟主机应当如何选购? 2023-05-01

- 企业网站建设使用虚拟主机 这几点要测一下 2016-08-06

- 虚拟主机被恶意攻击怎么办 2016-09-19

- 阿里云独享虚拟主机搭建个人网站步骤 2022-10-07

- 企业如何选择虚拟主机服务提供商? 2022-06-26

- 虚拟主机能用宝塔吗? 2021-03-13

- 站长建站选择云主机好还是虚拟主机好 2021-09-24

- 企业网站如何选择适合SEO的虚拟主机 2022-07-17

- 租用虚拟主机需要注意什么? 2022-07-26

- 关于服务器,虚拟主机及VPS的解释! 2019-09-09

- 同样可以建站,云服务器和虚拟主机的区别在哪? 2021-02-01

- 去那购买好的国外虚拟主机 2018-07-30